友情提示

本站部分转载文章,皆来自互联网,仅供参考及分享,并不用于任何商业用途;版权归原作者所有,如涉及作品内容、版权和其他问题,请与本网联系,我们将在第一时间删除内容!

联系邮箱:1042463605@qq.com

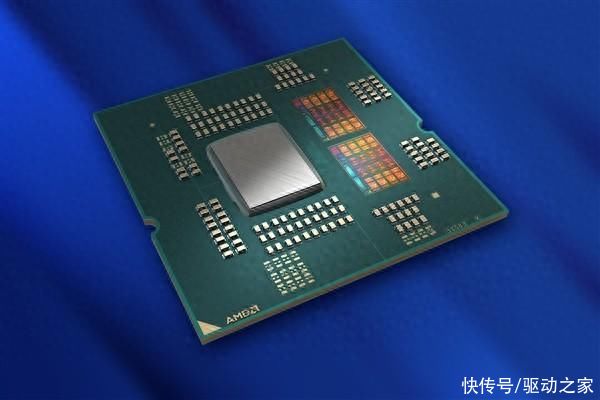

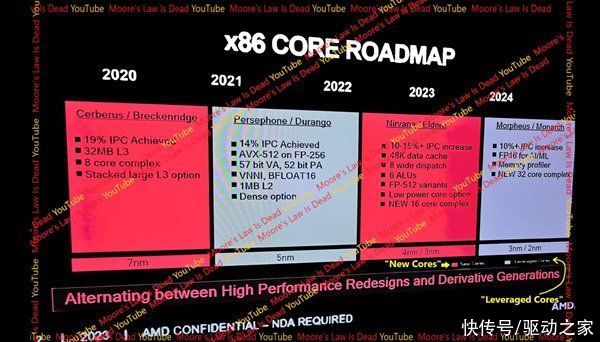

AMD Zen5性能暴涨40%的秘密:独享AVX-512指令集大升级

28

0

相关文章

近七日浏览最多

最新文章

标签云

intel

酷睿

xbox

gtx

显卡

快科技

高通

苹果

咸鱼翻身

英特尔酷睿

英特尔

处理器

cpu

gpu

bios

联想

ddr5

内存

moto

骁龙

ultra

英伟达

芯片

h6

哈弗

小红书

腾讯

锐龙

华硕

ibm

硬盘

固态硬盘

npu

小米

宾利

劳斯莱斯

无人机

车顶行李架

谷歌

美国司法部

搜索引擎

美国联邦

美国

奥迪q5l

q5l

余承东

奔驰s级

黄晓明

奥迪a8l

平板电脑

国产品牌

华为

华为nova

越南

印度

富士康

现实世界

电池容量

mac

周深

天猫

我是歌手

微软

董明珠

传祺gs5

辅助系统

墨西哥

广汽集团

道奇

广汽传祺

涡轮增压发动机

酷睿处理器

ipad

ios

m4

巴黎

雷军

电动自行车

中国留学生

日本

imax

周榜

蔚来

中国科技公司

小鹏汽车

李想

何小鹏

吉利

小鹏

人工智能

三星电子

钓鱼

隐藏功能

高德地图

大数据

ddr4

宁德时代

动力电池

磷酸铁锂电池